MEMS3 Debug Code Injection

MOTIVATION

As part of my ongoing quest to understand the internal working of the MEMS3 ECU, I have been working through disassembled code, slowly trying to unpick more and more of the key routines and to use the understanding gained to decipher what the various tables and scalar value found in the maps actually mean. In my day job as a software developer, I would usually be able to inspect the internal workings of code I had written by running it under a debugger. This would allow me to place break points at arbitrary code locations and pause the code execution at those points to inspect variable values etc. Sometimes this approach isn’t possible and it is not possible to run the code under a debugger and in those instances we usually have to resort to inserting debug code into the software to write out debugging information to a file, to the console or to another program. Although this approach is not as flexible as live execution under a debugger, it is still enormously useful. Although it takes more time using this method, it is usually possible to extract all of the information you need to understand a particular situation with patience.

So far with MEMS3 I have just been looking at disassembled source code in text form. It occurred to me that it would be so much better if I could actually debug a live running MEMS3 while it was running an engine.

Now I can’t see any practical way of executing the code on a live running engine on the road under a debugger in this situation, but it occurred to me that the second method above might just be doable …

OVERALL PLAN

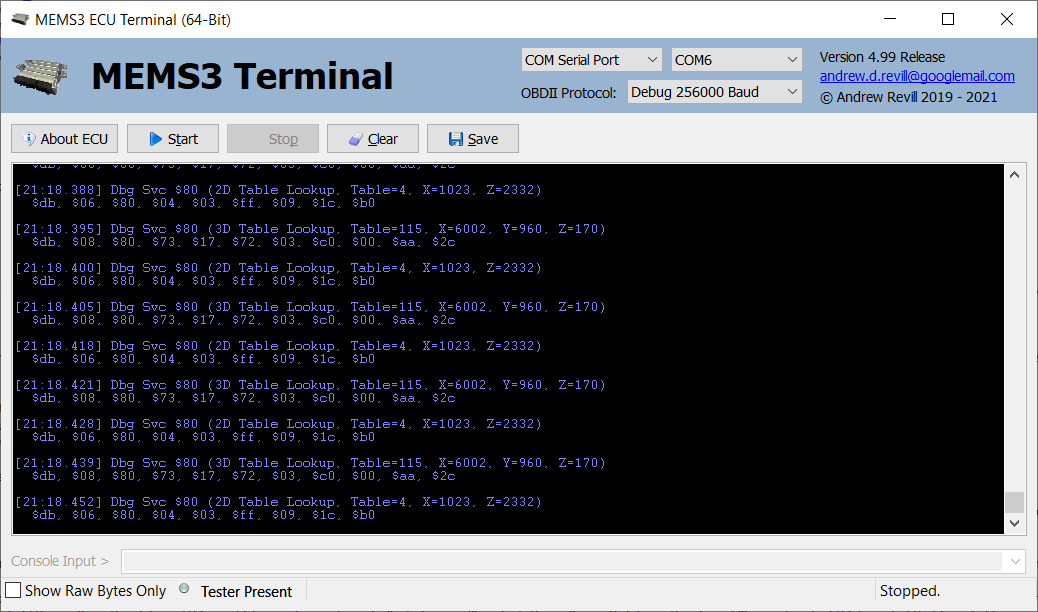

The overall plan was to provide a mechanism that allowed me to inject debug code into the firmware code at any point (or almost any point as there will be some restrictions), and to have that debug code be able to log out details of processor registers, memory variable contents etc. to the OBDII port where I could monitor it with a terminal program running on a PC or laptop connected through a simple OBDII serial cable. I would need to be able to inject code at an arbitrary number of points simultaneously and I would need to be able to specify what information I wanted to log out at each point.

There’s no way that wholesale modifications could be made to MEMS3 code and recompiled into a running state without access to the original development environments. But it seemed that it should be possible to write some small routines and patches directly in 68000 assembly language, or even generate them dynamically directly in 68000 opcodes, and then patch these into the existing code. My idea was that I could replace a few bytes at the point I wanted to debug with a jump into a debugging routine. This would add the required debugging information to the buffer to be written out to the OBDII port, then execute the instructions that had been overwritten and finally jump back to the next instruction in the original routine. This would place a few small restrictions on the points at which debug code could be injected:

· I could only insert debug code at the first byte of a machine code instruction.

· A JMP (permanent jump) or JSR (call to a subroutine) instruction to our code would occupy 6 bytes, so 6 consecutive bytes would get overwritten.

· Those 6 bytes may contain part of the next instruction. I would have to consider all operations at least partially contained within the 6 bytes to have been overwritten.

· The instructions overwritten must be capable of being executed at a different address. So short branches, access to memory locations relative to the program counter etc. would not be permitted.

None of these restrictions are so onerous as to make this not worth doing.

In order to do this I needed to find some EEROM addresses where I could safely write my injected program code and some RAM addresses I could safely use for variables, buffers etc.

EEPROM

The firmware EEPROM address space runs from $110000 to $139FFF. The actual size of the firmware code varies from one configuration to another but it typically ends around $1357FF, leaving addresses $135800 to $139FFF unused. This gives a contiguous block of 18 kilobytes of available EEPROM space. The last few bytes of this range are used by MEMS3Mapper to perform checksum corrections, but I think I am fairly safe to assume that addresses around $139000 onwards will otherwise be unused, and this gives me close to 4 kilobytes to play with, which is a lot more than I will need.

RAM

There are two modules within the 68336 microcontroller that provide RAM, namely SRAM (4 kilobytes of Standby RAM) and TPURAM (3.5 kilobytes of TPU ROM Emulation RAM). SRAM has the capability to provide low power standby battery backup, probably not used here. TPURAM has the ability to emulate the ROM in the TPU (Time Processing Unit) for development purposes, although this isn’t used in a running ECU.

Each of these blocks of RAM can be located anywhere within the memory address space. The base address of the SRAM memory is controlled by registers RAMBAH and RAMBAL. The base address of TPURAM memory is controlled by register TRAMBAR.

The main entry point routine of the boot loader handles basic hardware configuration and sets up both of these registers:

ROM:00100478 move.w #$10,(Local Boot

Variable TPURAM Register TRAMBAR).w

ROM:0010047E move.w #$100,(Local Boot

Variable TPURAM Register TRAMMCR).w

ROM:00100484 move.w #4,(Local Boot

Variable SIM Register CSBAR0).w

ROM:0010048A move.w #$3831,(Local

Boot Variable SIM Register CSOR0).w

ROM:00100490 move.w #4,(Local Boot

Variable SIM Register CSBAR1).w

ROM:00100496 move.w #$5831,(Local

Boot Variable SIM Register CSOR1).w

ROM:0010049C move.w #$1106,(Local

Boot Variable SIM Register CSBAR2).w

ROM:001004A2 move.w

#$1031,(Variable SIM Register CSOR2).w

ROM:001004A8 move.w #$4007,(Local

Boot Variable SIM Register CSBAR3).w

ROM:001004AE move.w #$7871,(Local

Boot Variable SIM Register CSOR3).w

ROM:001004B4 move.w #$5007,(Local

Boot Variable SIM Register CSBAR4).w

ROM:001004BA move.w #$7871,(Boot

Variable SIM Register CSOR4).w

ROM:001004C0 move.w #$FFE0,(Local

Boot Variable SIM Register CSBAR5).w

ROM:001004C6 move.w

#$BB71,(Boot Variable SIM Register CSOR5).w

ROM:001004CC move.w #0,(Local Boot

Variable SIM Register CSBAR6).w

ROM:001004D2 move.w #0,(Local Boot

Variable SIM Register CSOR6).w

ROM:001004D8 move.w #0,(Local Boot

Variable SIM Register CSBAR7).w

ROM:001004DE move.w #0,(Local Boot

Variable SIM Register CSOR7).w

ROM:001004E4 move.w #0,(Local Boot

Variable SIM Register CSBAR8).w

ROM:001004EA move.w #0,(Local Boot

Variable SIM Register CSOR8).w

ROM:001004F0 move.w #0,(Local Boot

Variable SIM Register CSBAR9).w

ROM:001004F6 move.w #0,(Local Boot

Variable SIM Register CSOR9).w

ROM:001004FC move.w #0,(Local Boot

Variable SIM Register CSBAR10).w

ROM:00100502 move.w #0,(Local Boot

Variable SIM Register CSOR10).w

ROM:00100508 move.w #0,(Local Boot

Variable SRAM Register RAMBAL).w

ROM:0010050E move.w #0,(Local Boot

Variable SRAM Register RAMBAH).w

ROM:00100514 move.w #0,(Local Boot

Variable SRAM Register RAMMCR).w

Once set, these are never changed. So RAMBAH and RAMBAL are set to 0 and TRAMBAR is set to $10. According to the 68336 User Manual, these values place the SRAM at addresses $0 to $FFF and the TPURAM at addresses $1000 to $1DFF. So in effect, even though coming from two different modules, there is a contiguous block of 7.5 kilobytes of fast RAM at addresses $0 to $1DFF.

I analysed the assembly language code for an NNN000160 (VVC 160 ECU) running ksr3p007 firmware using some software I wrote to produce a list of all RAM addresses in this range accessed by the code. This showed that the variable addresses are mostly closely stacked together (probably automatically by the compiler used) with a few notable exceptions:

· There’s an apparently unused block of 256 bytes ending at $200.

· There’s an apparently unused block of 254 bytes ending at $400.

· There are a few other “holes” where the memory doesn’t seem to be accessed.

· The variables are otherwise pretty much stacked together up to address $1405.

· Beyond that the RAM appears to be unused to address $1AFF, a gap of 1787 bytes.

· Between $1B00 and almost the top of RAM at $1DB3 there appear to be some larger structures as the only addresses referenced are in 32-byte increments.

When the ECU boots its initial behaviour is determine by the boot loader vector table which starts as follows:

ROM:00100000

dword_100000: dc.l $1400

ROM:00100000

ROM:00100004 dc.l Boot

Entry Subroutine Boot Loader Main Entry Point

ROM:00100008 dc.l Boot

Copy Vector Subroutine Enter Background Debugging Mode

ROM:0010000C dc.l Boot

Copy Vector Subroutine Enter Background Debugging Mode

ROM:00100010 dc.l Boot

Copy Vector Subroutine Enter Background Debugging Mode

ROM:00100014 dc.l $10279C

ROM:00100018 dc.l $10279C

ROM:0010001C dc.l $10279C

The first DWORD sets the initial value of the supervisor stack pointer register SP to $1400. The second DWORD is the address of the boot loader main entry point routine, which starts off as follows:

ROM:0010041C

; ---------------------------------------------------------------------------

ROM:0010041C cmpa.l #$1400,sp

ROM:00100422 beq.s loc_10043A

ROM:00100424 cmpi.l #$12345677,d4

ROM:0010042A beq.s loc_100434

ROM:0010042C cmpi.l #$12345678,d4

ROM:00100432 bne.s loc_10043A

ROM:00100434

ROM:00100434

loc_100434:

ROM:00100434 bra.l loc_100520

ROM:0010043A

;

---------------------------------------------------------------------------

This tests whether the stack pointer is equal to $1400 as the first step, which initially confused me as the stack pointer would have been set to this immediately before calling this routine, however I then noticed that very early on in the initialisation code it does this:

ROM:00100526

ROM:00100526

loc_100526:

ROM:00100526 movea.l #$200,sp

This sets the stack pointer to $200. So it looks as though the check for $1400 is to determine whether the routine is being executed from cold after the ECU boots up or whether it has been reset by a jump back to the main entry point (although I haven’t yet found this in code, and I believe the Software Watchdog System would perform a full RESET if the firmware locked up).

It’s a very similar story when the boot loader transfers control to the main firmware. There’s a firmware vector table which starts as follows:

ROM:00110000

dword_110000: dc.l $1400

ROM:00110000

ROM:00110004 dc.l Entry

Subroutine Firmware Main Entry Point

ROM:00110008 dc.l Copy

Vector Subroutine Enter Background Debugging Mode

ROM:0011000C dc.l Copy

Vector Subroutine Enter Background Debugging Mode

ROM:00110010 dc.l Copy

Vector Subroutine Enter Background Debugging Mode

ROM:00110014 dc.l $115F22

ROM:00110018 dc.l $115F22

ROM:0011001C dc.l $115F22

And the firmware main entry point routine starts off as follows:

ROM:0011562E

; =============== S U B R O U T I N E

=======================================

ROM:0011562E

ROM:0011562E

; Attributes: noreturn

ROM:0011562E

ROM:0011562E

sub_11562E:

ROM:0011562E move.l #dword_110000,d0

ROM:00115634 movec d0,vbr

ROM:00115638 movea.l #$400,sp

ROM:0011563E bsr.l Subroutine

sub_119524

ROM:00115644 clr.l d0

ROM:00115646 move.l #$1B00,d1

ROM:0011564C movea.l d0,a0

This updates the Vector Base Register to $110000 which is the address of the firmware vector table, the proceeds as for the boot loader, and shortly afterwards does this:

ROM:001156B0

ROM:001156B0

loc_1156B0:

ROM:001156B0 movea.l #$400,sp

This sets the stack pointer to $400.

I scanned the full assembly code for anywhere that the stack pointer register SP was updated and found only the following lines. The first of these is the line I found above in the boot loader main entry routine, the second one is the line I found in the firmware main entry routine and the third one is also in the firmware and resets the stack pointer to the same address $400.

ROM:00100526 movea.l #$200,sp

ROM:00115638 movea.l #$400,sp

ROM:001156B0 movea.l #$400,sp

So it appears the 256 byte gap in the RAM addresses accessed ending at $200 is the boot loader stack and the 254 byte gap in the RAM addresses accessed ending at $400 is the firmware stack (on a 68000 family microprocessor, the stack grows downwards to lower addresses so SP is initialise to point to the top of the otherwise unused memory block).

So in summary there is a boot loader stack ending at $200, we have a firmware stack ending at $400, packed around these there are variables up to $1405 and then some other structures of mostly 32 and 64 bytes in the last part of RAM from $1B00 onwards. Now $1405 is not a round number and I don’t think it has any special significance; it’s just that the actual physical RAM on the chip has more capacity than the programming of the ECU actually uses, and $1405 is where the used portion ends (with $1B00 onwards being used for some special purpose).

This leaves a block of 1787 bytes between $1405 and $1B00 which look they are unused and possibly available for me to use for my own purposes.

Now all of this is based on ksr3p007 firmware running on NNN000160 hardware and boot loader. It can’t be guaranteed that every other MEMS3 configuration will be exactly the same, but from what I’ve seen they all have so much in common that I am probably safe to make the following assumptions:

· The general structure of the lower RAM addresses stacking up will be fixed across all MEMS3 configurations.

· The usage of $1B00 onwards for some special purpose is also likely to remain fixed.

· Some ECUs will probably use fewer variables and so the RAM addresses used will end below $1405.

· Some ECUs may have more variables and so the RAM addresses used will end above $1405, although the differences in memory are likely to be relatively small as the vast majority of the code base is common.

So for example if I choose to work on the basis that RAM addresses from $1A00 or $1900 are overwhelmingly likely to be available in any MEMS3 configuration, this would give me either 256 or 512 bytes to play with, which is more than I will need.

FIRST APPROACH

The standard OBDII protocols run at 9600 or 10400 Baud. This limits the rate at which debug information could be logged out. My initial thought was that I would have to write a complete interrupt-driven read and write communication system and effectively take complete control of the QSM/SCI module which drives the OBDII port, replacing the existing interrupt handlers with my own. However, there were two problems with this. Firstly it was going to be a difficult job to code something like directly in assembly language, especially when I was new to 68000 assembly. Secondly, there were places in the main code execution loop which indirectly accessed the QSM Data Register and QSM Status Register and these would be hard to patch out. A quick test of some minimal replacements for the interrupt handlers just caused the ECU to crash and it appeared that there was an element of polling going on as well as responding to interrupts.

A little more digging turned up the following two subroutines:

ROM:00112234

; =============== S U B R O U T I N E

=======================================

ROM:00112234

ROM:00112234

sub_112234:

ROM:00112234

ROM:00112234 move.l (Scalar $13C124),d0

ROM:00112238 divu.l #$51400,d0

ROM:00112240 move.w d0,(Variable QSM Register SCCR0).w

ROM:00112244 rts

ROM:00112244

; End of function sub_112234

ROM:00112244

ROM:00112246

; =============== S U B R O U T I N E

=======================================

ROM:00112246

ROM:00112246

sub_112246:

ROM:00112246

ROM:00112246 move.l (Scalar $13C124),d0

ROM:0011224A divu.l #$4B000,d0

ROM:00112252 move.w d0,(Variable QSM Register SCCR0).w

ROM:00112256 rts

ROM:00112256

; End of function sub_112246

ROM:00112256

These are the only two places in the whole of the firmware where register SCCR0 is modified. This is Control Register 0 for the SCI and sets the Baud rate. According to the MC68336 User Manual, the Baud rate is (System Clock Frequency) / 32 / SCCR0. In these routines a scalar value is read from the map and divided by a constant, either $51400 or $4B000. These are just the hexadecimal representations of the two standard Baud rates 10400 and 9600, multiplied by 32. So the calculation looks to be correct according to the definitions in the User Manual if the scalar value is programmed with the system clock frequency. Checking the map, the 4-byte Long value at this address was $00F8D400 or 16,307,200 decimal. I knew the system clock frequency was nominally 16Mhz, so this made sense.

These are simple self-contained routines that do nothing else other than set the Baud rate and so should be easy targets to scan for and patch in the firmware.

I did some experiments patching the constant for the Rover BMW protocol from 9600 Baud to high Baud rates. I then modified the code in my MEMS3 Mapper application to talk to the ECU at the higher Baud rate and everything worked fine up to 38,400 Baud (with the constant patched to $12C000). Beyond this, it would not communicate, despite the fact that both the PC / FTDI serial cable and the QSM/SCI in the ECU were capable of going to much higher Baud rates. It was only when I came to work on the assembly language files later that I realised why:

· For 9600 Baud, the calculation 16307200 / 32 / 9600 gives 53.08. As this is an integer constant we are forced to use 53, which gives an actual Baud rate of 9615. This is only a 0.15% error and communication will be fine.

· For 38400 Baud, the calculation 16307200 / 32 / 38400 gives 13.27. Again as this is an integer constant we are forced to use 13, which gives an actual Baud rate of 39200. This is a 2% error and communication should still just about be OK (up to about 3% difference between send and receive clock rates is acceptable).

· For 57600 Baud, the calculation 16307200 / 32 / 57600 gives 8.84. The closest integer constant we can use is 9, but a simple integer division as used in the code will round down and so yield 8, which gives an actual Baud rate of 63700. This is a 10.5% error and communication will not be possible.

I checked the specifications for the FT232RL chip in my programming cable, and that generates Baud rates by dividing in internal clock frequency of 3 MHz by the sum of an integer divisor and fractional divisor, which can take various fixed values including ¼, ½, ¾ and some others. A quick check showed that a nominal standard value of 256,000 Baud should be possible:

· The QSM/SCU in the ECU would actually run at 16307200 / 32 / 2 = 254800 Baud.

· The FT232RL serial cable would actually run at 3000000 / 11.75 = 255319 Baud.

· The error / difference between them would be only 0.2%, and communication should therefore be reliable.

One thing that still concerned me was the direct access to the SCI registers that I found in routines called from within the main program loop. The whole ECU firmware is written as one large loop that executes repeatedly. The main firmware entry point routine initialises various aspects of the hardware not fixed by the boot loader than jumps straight into the main program loop. This starts by notifying the Software Watchdog Service that it is still operating normally then calls a whole bunch of nested routines which for a large collection of state machines, and which handle all of the ECUs executive functions and calculations.

With some more digging through the OBDII code, although I didn’t understand quite a lot of what I was reading, the overall structure started to come to me and several things told me there was a problem:

· The ECU seemed to be using the same buffer for sending and receiving messages.

· The process of sending a message seemed to involve building the message up in a buffer (and always right at the start of the buffer), then setting a count variable to say how many bytes from the buffer were to be sent, then writing the first byte to the SCDR register. From here an interrupt was generated when the first byte had finished sending, and the interrupt handler then wrote the next byte to the SCDR register. This continued until the count was 0.

All of this suggested that the routines expected to receive a single message, then send a single response. There was no possibility of sending and receiving overlapping as they used the same buffer, and it really wasn’t structured to allow more data to appended to the sending queue while a message was being sent; although the bytes of a message were queued in a buffer and sent in the background through interrupt handlers, multiple messages could not be queued. This all works find for the OBDII protocols but not for a debugging system where debug information may be appended to the queue at any time.

So it looked like there was nothing for it but to bite the bullet and write my own communications software for it.

SECOND APPROACH

The first challenge was then to ensure that existing code in the ECU wouldn’t fight against what I was doing. I needed to find a way to completely knock out all access to the QSM/SCI from the existing code, whilst leaving the engine management functions intact and functioning normally. I set about this by making a list of all of the registers that were associated with the QSM/SCI (these being the control registers SCCR0 and SCCR1, the status register SCSR and the data register SCDR) and using my MEMS3 Browser application to track down all of the references to these in the code.

My first idea was simple. Unfortunately a bit too simple. All of the registers are accessed as memory locations ($FFFFFC08, $FFFFFC0A, $FFFFFC0C and $FFFFFC0F). My idea was to replace all references to these addresses with references to harmless addresses in RAM. The ECU would then just read and write to and from unused memory rather than to and from the QSM/SCI control registers. The ECU would be none the wiser but the QSM/SCI would not be touched and would be free for me to manipulate in my own code. However, when I came to look at the binary instructions that wrote to these addresses I was initially confused until I learned about 68000 short addressing.

Here’s an instruction to write a byte to the SCDR:

ROM:001122C2 move.w #$55,(Variable OBDII Port Data Register).w

The address associated with the SCDR is $FFFFFC0F, but the bytes for this instruction only specify the lower word $FCOF. The address is then sign-extended, so if the high bit of the lower word is 1 then the higher word is $FFFF and if the high bit of the lower word is 0 then the higher word is $0000. This means that these instructions can only access the first 32 kilobytes of the memory space $00000000-$00007FFF or the last 32 kilobytes of the memory space $FFFF8000-$FFFFFFFF. This works in the ECU as the registers are all mapped to the top few addresses. It did allow me to covere the whole of the RAM address space, but unfortunately all I found was that the existing code got very unhappy if all it read from the registers was the data it last wrote to them and the ECU just kept rebooting.

So the second idea was to assume that if a subroutine was handling OBDII processing, then hopefully the code was well enough structured that the subroutine was dedicated exclusively to OBDII functions and there wasn’t a random bit of engine code in the same subroutine. On this basis, there was a chance that I would be able to disable a number of entire subroutines (by overwriting the first instruction with RTS in the case of a normal subroutine or RTE in the case of an interrupt or exception vector) and still have a functioning ECU.

The list of subroutines which accessed the QSM/SCI was initially quite long:

|

Address |

FFFFFC08 |

FFFFFC0A |

FFFFFC0C |

FFFFFC0F |

|||

|

Register |

SCCR0 |

SCCR1 |

SCSR |

SCDR |

|||

|

Vectors |

|||||||

|

$111680 |

|||||||

|

$115E30 |

Ref. |

Ref. |

|||||

|

Subroutines |

|||||||

|

$1116D0 |

Ref. |

||||||

|

$1116D6 |

Ref. |

Ref. |

|||||

|

$116AF6 |

Ref. |

Ref. |

|||||

|

$118C92 |

Ref. |

Ref. |

|||||

|

$132C8A |

|||||||

|

$111D4C |

Ref. |

||||||

|

$112172 |

Ref. |

Ref. |

|||||

|

$1121EE |

Ref. |

||||||

|

$112210 |

Ref. |

||||||

|

$112234 |

Ref. |

||||||

|

$112246 |

Ref. |

||||||

|

$112278 |

Ref. |

Ref. |

|||||

|

$1122C2 |

Ref. |

||||||

|

$1122CA |

Ref. |

||||||

|

$1122D2 |

Ref. |

||||||

|

$1122DA |

Ref. |

||||||

|

$112318 |

Ref. |

||||||

|

$116DAA |

Ref. |

Ref. |

|||||

|

$11862E |

Ref. |

Ref. |

|||||

|

$11878C |

Ref. |

Ref. |

|||||

|

$125030 |

Ref. |

||||||

|

$1254A4 |

Ref. |

||||||

|

$1254DE |

Ref. |

||||||

|

$12558C |

Ref. |

||||||

|

$134816 |

Ref. |

||||||

|

$13482A |

Ref. |

||||||

But with a bit of investigation using the dependency tree mapping in my MEMS3 Browser application I was able to see that these mostly formed trees, where one routine which accessed the OBDII port was actually often just a child subroutine of another parent subroutine which also accessed the OBDII port, so in fact with some planning I only needed to disable a small number of routines:

|

Address |

FFFFFC08 |

FFFFFC0A |

FFFFFC0C |

FFFFFC0F |

|||||||

|

Register |

SCCR0 |

SCCR1 |

SCSR |

SCDR |

|||||||

|

Vectors |

Fix |

||||||||||

|

$111680

(QSM Int. Vector) |

RTE |

$111680

$4E |

(OR

Replace Vector) |

||||||||

|

$111681

$73 |

|||||||||||

|

$115E30

(Unknown Int. Vect.) |

Ref. |

Ref. |

RTS |

$118C26

$4E |

(RTS

from Switch Subroutine) |

||||||

|

$118C27

$75 |

|||||||||||

|

Subroutines |

Referenced

By |

Fix |

|||||||||

|

$1116D0 |

Ref. |

Vect.

$115E30 |

RTS |

$1116D0

$4E |

|||||||

|

$1116D1

$75 |

|||||||||||

|

$1116D6 |

Ref. |

Ref. |

Main

Entry |

RTS |

$1116D6

$4E |

||||||

|

$1116D7

$75 |

|||||||||||

|

$116AF6 |

Ref. |

Ref. |

Vect.

$115E30 |

RTS |

$116AF6

$4E |

||||||

|

$116AF7

$75 |

|||||||||||

|

$118C92 |

Ref. |

Ref. |

Vect.

$115E30 |

RTS |

$118C92

$4E |

||||||

|

$118C93

$75 |

|||||||||||

|

$132C8A |

Master

Update |

RTS |

$132C8A

$4E |

||||||||

|

$132C8B

$75 |

|||||||||||

|

Referenced Only by the Above |

Ref. By |

||||||||||

|

$111D4C |

Ref. |

$111680 |

|||||||||

|

$112172 |

Ref. |

Ref. |

$111680 |

||||||||

|

$1121EE |

Ref. |

$1116D6 |

|||||||||

|

$112210 |

Ref. |

$1116D6 |

|||||||||

|

$112234 |

Ref. |

$1116D6 |

$111680 |

||||||||

|

$112246 |

Ref. |

$1116D6 |

$111680 |

||||||||

|

$112278 |

Ref. |

Ref. |

$1116D0 |

$1116D6 |

$111680 |

||||||

|

$1122C2 |

Ref. |

$1116D6 |

|||||||||

|

$1122CA |

Ref. |

$1116D6 |

|||||||||

|

$1122D2 |

Ref. |

$1116D6 |

|||||||||

|

$1122DA |

Ref. |

$1116D6 |

|||||||||

|

$112318 |

Ref. |

$111680 |

|||||||||

|

$116DAA |

Ref. |

Ref. |

$111680 |

||||||||

|

$11862E |

Ref. |

Ref. |

$111680 |

||||||||

|

$11878C |

Ref. |

Ref. |

$111680 |

||||||||

|

$125030 |

Ref. |

$1116D6 |

$111680 |

||||||||

|

$1254A4 |

Ref. |

$1116D6 |

$111680 |

||||||||

|

$1254DE |

Ref. |

$1116D6 |

$111680 |

||||||||

|

$12558C |

Ref. |

$1116D6 |

|||||||||

|

$134816 |

Ref. |

$132C8A |

|||||||||

|

$13482A |

Ref. |

$132C8A |

|||||||||

There were two interrupt vectors to disable, namely $111680 which was assigned to interrupt number $50 in the interrupt vector table and interrupt number $50 was assigned to the QSM in code, and $115E30 which was assigned to interrupt number $52 in the interrupt vector table. There were the five subroutines to disable. Now although the QSM is assigned interrupt number $50, the QSM contains two submodules, the SCI (which drives the OBDII port) and the QSPI (Queued Serial Peripheral Interface). The SCI uses the assigned interrupt number $50 and the QSPI uses the next number $51. The vector for $51 is unassigned in the vector table suggesting that the QSPI is unused in the MEMS3 ECU. I couldn’t find any references in code to interrupt number $52 but is clearly being assigned somehow, and it broke the rule I proposed earlier that OBDII subroutines are likely to be exclusively OBDII-related, as disabling this interrupt vector left the ECU engine management function crippled. So instead I had to step one level down the tree of subroutines and disable the code within a SWITCH subroutine inside the vector routine itself and a three other subroutines which it called.

In the end I had to patch over just 14 bytes:

$111680 $4E

$111681 $73

$118C26 $4E

$118C27 $75

$1116D0 $4E

$1116D1 $75

$1116D6 $4E

$1116D7 $75

$116AF6 $4E

$116AF7 $75

$118C92 $4E

$118C93 $75

$132C8A $4E

$132C8B $75

I then wrote the firmware to the ECU using MEMS3 Mapper and the result was as I hoped. The ECU still ran the engine perfectly normally, but was completely silent in terms of OBDII communications. No outgoing data and all incoming data silently ignored. Otherwise it seemed perfectly happy. Once the ECU had loaded its firmware on boot, it was now effectively “bricked” as you could not communicate with it to update the programming further, but luckily my MEMS3 Mapper tool now has a “Recover Bricked ECU” function which sends a special code to the boot loader to stop it loading the firmware, and the boot loader code was still intact. So recovery was just one click each time I needed to reprogram the ECU.

Now poking individual bytes into memory locations was OK just to prove a point, but obviously to do any serious programming I was going to need a rather more functional setup. I searched on Google and found the EASy68K assembler. It’s nothing fancy, not a fully-featured IDE or anything, just a basic 68000 assembler with a simulator to test bits of code, but it looked like it would do the job and it was free, so I downloaded a copy and used it to put together the starts of a project. Here is the listing up to this point. It basically just declares RTS instructions at the addresses determined above:

*

START OF CODE

START:

*

APPLY PATCH - DISABLE NATIVE QSM/SCI ACCESS

*

*

The instructions below are patched into specific locations within the firmware

to

*

effectively disable access to the QSM/SCI. RTS instructions are used to replace

*

existing instructions in order to force early return from a subroutine. In most

*

cases the first instruction of the subroutine is replaced, disabling the

subroutine

*

entirely.

ORG $118C26 * Subroutines, return with RTS. * Firmware ksr3p007 only!

rts

ORG $1116D0

rts

ORG $1116D6

rts

ORG $116AF6

rts

ORG $118C92

rts

ORG $132C8A

rts

END START

GETTING CODE INTO THE ECU

I was using my MEMS3 Mapper application for reading and writing to ECUs. The assembler produced two output files, a .L68 listing file (which was really for human consumption) and a .S68 file which on inspection was in Motorola S-Record format. This is a fairly simple file format to read, so I added support for importing firmware patches from .S68 files into my MEMS3 Mapper application. I added in quite a bit of checking code too, to make sure that the .S68 file was fully understood and decoded and to make sure that it could only be loaded against the firmware version for which it was written, as it was based on absolute addresses which would vary between firmware versions.

When the MEMS3 Mapper application loads a firmware patch from a .S68 file, it only applies changes which fall within the firmware memory address space and raises an error if it finds anything which falls outside of the firmware. It initially copies the firmware into a buffer, then overwrites any bytes specified in the S-Record file. It then copies the data back from the buffer into the firmware provided that the .S68 loaded correctly. Before doing this, it compares the Firmware ID field in the buffer with that in the firmware and rejects the patch if they are different. This allowed me to include the Firmware ID field in my patch, and the loader would only then let me load it against the correct firmware.

I added the following lines at the top of my listing. Notice that each character of the firmware ID is repeated twice; this is correct, this is how the ECU stores the firmware ID for some reason which I do not know:

*

FIRMWARE COMPATIBILITY CHECK

*

*

This writes the firmware ID into the location at which it is normally stored

within the

*

firmware. This allows the MEMS3 Mapper S-Record loader code to verify that the

patch is

*

being applied to the firmware version for which it was written.

*

*

Many of addresses specified as constants within this file are specific to a

firmware

*

version. Constants annotated "Firmware ksr3p007 only!" are only applicable

to the

*

firmware version ksr3p007.

ADDR_FIRMWARE_ID: EQU $110400

ORG

ADDR_FIRMWARE_ID

DC.B 'kkssrr33pp000077' * Firmware ksr3p007 only!

INITIALISING EVERYTHING

Once I started putting some proper code together, I was clearly going to need to initialise things as the ECU booted up. In order to do this, I was going to have to patch into the main initialisation code of the existing firmware. Looking at the main entry point routine of the firmware using my MEMS3 Browser tool, I could see this section (all of the comments are added by me):

ROM:001156B0

loc_1156B0:

ROM:001156B0 movea.l #$400,sp

ROM:001156B6 move.w sp,(Variable $53E).w

ROM:001156BA movea.l #word_13C000,a5 ; point

register a5 to start of map

ROM:001156C0 move.l a5,(Variable Map

Base Address).w

ROM:001156C4 bsr.w Copy Point

Subroutine sub_1158BE

ROM:001156C8 bsr.l Subroutine

sub_116056

ROM:001156CE clr.w (Variable $4CC).w

ROM:001156D2 bsr.l Subroutine

sub_119524

ROM:001156D8 bsr.l Point Subroutine

sub_110D06

ROM:001156DE bsr.l Copy Point Subroutine

nullsub_52

ROM:001156E4 bsr.l Copy Point

Subroutine sub_115E1E

ROM:001156EA bsr.l Point Subroutine

sub_11086A

ROM:001156F0 bsr.l Point Subroutine

sub_11143E

ROM:001156F6 bsr.l Point Subroutine

sub_111422

ROM:001156FC bsr.l Point Subroutine

sub_135582

ROM:00115702 move.b #0,(Variable SIM

Register PFPAR).w

ROM:00115708 move #$2000,sr

ROM:0011570C

ROM:0011570C

; This is the start of the main program loop.

ROM:0011570C

ROM:0011570C

main_program_loop:

ROM:0011570C move.b #$55,(Variable

Software Watchdog Service Register).w ; reset

watchdog service step 1 of 2

ROM:00115712 move.b #$AA,(Variable Software

Watchdog Service Register).w ; reset watchdog

service step 2 of 2

ROM:00115718 movea.l (Variable Map Base Address).w,a5 ; point register a5 to start of map

ROM:0011571C addq.w #1,(Local

Variable $C1A).w

ROM:00115720 bvc.s loc_115728

ROM:00115722 move.w #$8000,(Local

Variable $C1A).w

The first few lines are the end of the ECU initialisation code which executes as the firmware boots up. Once that is complete it drops into the main program loop, which just executes over and over again. The first thing the main program loop does is to reset the watchdog service to tell it that it’s still alive and well and running normally (if this isn’t done within a certain timeframe the watchdog service will reboot the ECU).

The last but one line of the initialisation code at address $115702 cleared one of the microcontroller peripheral registers to 0. At this point all of the normal initialisation of the ECU is complete and it is ready to start normal operation in the main program loop, so this is where I need to make any configuration changes without them being overwritten by anything. The next instruction is at address $115708, so this instruction occupies 6 bytes, which is exactly the same size as a JSR (Jump to Subroutine) instruction. And it’s relocatable (there’s nothing about it that accesses data relative to the address of the instruction, so it will work just the same from any memory address). So all I needed to do was to replace this one instruction with a call to my own initialisation code, and make sure that within my own code I executed the one instruction I had overwritten before returning.

I added in some constants to set where everything was going to go in memory:

*

CONSTANTS - BASE ADDRESSES

*

*

These constants declare the base addresses for the RAM and ROM blocks which we

have

*

chosen to use. They also declare the base address of the firmware vector table

which is

*

found at the very start of the firmware address space, the base address of the

map and

*

the base address for the table index in the map.

ADDR_BASE_RAM_DATA: EQU $1900 * Base RAM data

address. * Firmware ksr3p007 only!

ADDR_BASE_ROM_CODE: EQU $139040 * Base ROM code

address. * Firmware ksr3p007 only!

ADDR_BASE_VECTORS: EQU $110000 * Base address for vectors.

A constant to declare where I was going to patch in the call:

*

CONSTANT - INITIALISATION PATCH ADDRESSES

*

*

This constant declares the address within the firmware initialisation routine

where we

*

have chosen to patch in a call to our own initialisation routine.

PATCH_INI_JMP: EQU $115702 * Firmware

ksr3p007 only!

The basic outline of an initialisation routine:

*

PATCH ROUTINE FOR INITIALISATION

*

*

The _patch_initialise subroutine initialises the debug patch. It is called from

the

*

main firmware initialisation routine by overwriting a MOVE.B #0,($FFFFFA1F).W

*

instruction with JSR _PATCH_INITIALISE. The _patch_initialise subroutine then

*

executes the relocatable instruction which was overwritten then proceeds to

perform

*

its own initialisation tasks.

*

*

PARAMETERS:

* Void.

*

RETURNS:

* Void.

_patch_initialise:

OPT NOWAR * Execute

instruction replaced by patch.

move.b

#0,($FFFFFA1F).w

OPT WAR

REG_PATCH_INI: REG d0-d1,ao-a1,sr * Save registers (PATCH: Preserves ALL).

movem.l

REG_PATCH_INI,-(sp) * Non-scratch

registers preserved by subroutines.

****

INITIALISATION CODE GOES HERE ****

movem.l

(sp)+,REG_PATCH_INI * Restore

registers.

rts

And the actual patch to replace the instruction with a call to this routine:

*

APPLY PATCH - INITIALISATION

*

*

The _patch_initialise subroutine initialises the debug patch. It is called from

the

*

main firmware initialisation routine by overwriting a MOVE.B #0,($FFFFFA1F).W

*

instruction with JSR _PATCH_INITIALISE. The _patch_initialise subroutine then

*

executes the relocatable instruction which was overwritten then proceeds to

perform

*

its own initialisation tasks.

ORG PATCH_INI_JMP * Patch address.

jsr

_patch_initialise * Patch routine.

Notice that the first thing I did within my initialisation routine was to execute the MOVE.B #0,($FFFFFA1F).W instruction which replaced the one overwritten by the call. In the disassembled listing shown earlier the register address $FFFFFA1F was decoded and displayed as Variable SIM Register PFPAR but they both refer to the same things. I then had to take care to ensure that the code I was patching in did not disturb any of the register values set up by the existing code, so I pushed all registers to the stack before any of my code and restored them all afterwards.

REPLACING THE OBDII ROUTINES

Some searching on the internet turned up this: https://www.nxp.com/docs/en/application-note/AN1724.pdf “Implementing SCI Receive and Transmit Buffers in C”. Freescale (previously the semiconductor division of Motorola, later merged with NXP, who produced the MC68336 microcontroller chip) had produced an example, written in C, of a ring-buffered receiver and transmitter for the 68336 SCI. Now this should really make things a lot easier. It was in the form of generic library functions to initialise the SCI, query the status, read received bytes and queue up bytes for writing and seemed to to be exactly what I needed. Being interrupt driven, the actual transmission happened in the background and the code sending the message was not delayed waiting for the transmission to complete.

All I needed to do (in theory …) was to find a C compiler for the 68000 CPU that would allow me to set the based address for RAM and EEPROM to place them in the free areas identified earlier.

Of course nothing is ever that simple. All of this technology is getting a bit long in the tooth now, but luckily the 68000 was very well supported and there is still plenty of stuff available for free on the net, however there were so many different flavours in the 68000 family that a lot of the different tools out there are just not compatible. In the end I had to go through the following process to end up with something that at least looked like it might work:

· I used the online C to 68000 Assembly version of Compiler Explorer: https://franke.ms/cex/. I compiled the C file as though it was for an Amiga computer, using the g++-10.2.1b compiler settings.

· This compiled to Assembly language rather than right down to binary code, but this was ideal as I could then combine this with the other assembly code I was writing and feed it through one common assembler.

· I then used the EASy68K assembler as before.

On inspection, the assembled code had some problems:

· One of the routines was an interrupt vector. These need to be compiled with certain particular features. In particular they must preserve the values of all registers (as they could get executed asynchronously in the middle of other random code being executed, so they must make sure that when they return it is as though they had never been called). Interrupt vector routines also need to return with an RTE (Return From Exception) instruction instead of an RTS (Return from Subroutine) instruction, to exit supervisor mode and restore the status register. The C code marked this routine with #pragma TRAP_PROC which was supposed to instruct the compiler to compile it as a vector, but the online compiler clearly hadn’t understood this and it was compiled as a regular subroutine. It was fairly easy to edit in the required changes by hand.

· The assembly language produced by the compiler used mangled subroutine names, which the assembler rejected as being too long. These had to be manually edited down to shorter names acceptable to the assembler.

· The assembly language produced by the compiler was intended to feed into a linker, and therefore used address-independent pseudo-opcodes like JBSR for a jump (which the linker would convert to BSR for a short branch or JSR for a long jump once it knew where everything was going in memory). This was fairly easy to work around, manually editing all of the pseudo-opcodes into real opcodes.

· The syntax used by the compiler and assembler differed slightly, for example the compiler produced LINK.W opcodes where the assembler expected the syntax LINK. Again these were all easily edited by hand.

· All of the meaningful constants, such as QSM register addresses, had been lost during the process of compilation and appeared in the code as meaningless numbers. This was compounded by the fact that addresses for registers such as $FFFFFC00 had been converted to NEGATIVE numbers, in this case -1024. Whilst technically correct, this was not consistent with the format used elsewhere throughout the assembly language code I was working with for the ECU and made the code difficult to read. Once again, I had to manually work my way through the assembled code defining constants and editing them in where used. This was particularly important as some of the “constants” were likely to change in the future, for example the buffer sizes I had chosen. I needed to ensure that these changes would be applied consistently.

· The design used the same buffer size for the transmit and receive buffers. This constant was compiled into the routines that queried the queue status. For my used case this was extremely wasteful of RAM which was a previous resource. Ideally I needed a large transmit buffer to allow me to log a lot of messages in quick succession without overrunning, but I did not need a similarly large receive buffer. In fact for the initial plans I had in mind I didn’t really need receive functionality at all but no doubt it will come in useful in the future so I decided to retain it. I had to do some work to do to parameterise the queue status function and separate out the transmit and receive buffer sizes.

CALLING CONVENTIONS

The biggest problem with the assembled code quickly became obvious during initial testing.

The standard calling convention on 68000-based systems (in fact about the only calling convention I can find documented anywhere) is that registers d0, d1, a0, a1 are “scratch registers”, which means that you have to assume that after calling a subroutine these registers will have been overwritten. All other registers must be preserved by subroutines, which is generally done using MOVEM instructions to push them onto the stack. Parameters are passed to subroutines on the stack. Local variable storage is on the stack, with a stack frame being allocated for each subroutine using LINK and UNLK instructions.

The 68000 has a 24-bit address bus and so can access 16 megabytes of memory. All of the above works fine on an Atari or an Amiga, where RAM is plentiful. But as I have already established, here there is only 7.5 kilobytes for the whole system, and much of that is allocated to specific purposes. The amount of RAM left allocated for the stack is absolutely tiny, especially when handling an interrupt where all of the registers get stacked. The apparent hole in the memory allocation used for the stack was only 254 bytes in size. Even just pushing the 8 data registers and 8 address registers when handling an interrupt would use 64 bytes which is a quarter of the total stack space. You really can’t nest anything very deeply using a protocol that is stack-hungry. Everything I tried to do with the assembled code above eventually led to stability problems and crashes, and in nearly every case the cause turned out to be the same; I had simply run out of stack space and the stack was overwriting other things in RAM.

A quick analysis of the disassembled code for one particular firmware revealed that there were 1322 subroutines. The LINK and UNLK instructions, which I expected to be used in most subroutines for allocating a stack frame, were used a total of ONCE across the whole of the code. The MOVEM instruction, which I expected to be used in most subroutines for preserving registers, was used for less frequently than expected. The standard 68000 calling convention was just far too stack-hungry to use with this little RAM available in an embedded system. I was clearly going to have to do a lot of work to rework everything to work in a way more similar to rest of the ECU code.

This would involve combing through all of the compiled code by hand, stripping out all of the stack frames, changing all of the parameter access from stack-based to register based and replacing all of the local variables allocated on the stack with static RAM addresses.

After a lot of manual editing and formatting, I ended up with the following assembly language listing:

*

CALLING CONVENTION

*

*

The standard 68000 calling convention is that registers d0-d1 and a0-a1 are

scratch

*

and must be assumed to be trashed after calling a subroutine. All other

registers

*

must be preserved by the callee. Parameters are passed on the stack in right to

left

*

order. Stack frames are used to allocate local variable space on the stack.

Results

*

are returned in register d0.

*

*

HOWEVER: This calling convention is "stack-hungry" and the stack

space available here

*

is very small. None of the native code within the ECU boot loader or firmware

follows

*

this calling convention. Attempting to follow this convention in this code just

*

resulted in stack overflows and crashes. The code in this file is therefore

written

*

to be more like the native ECU and follows the following convention:

*

*

Registers d0-d1 and a0-a1 AND ANY REGISTERS IN WHICH PARAMETERS ARE PASSED TO A

*

SUBROUTINE are scratch and must be assumed to be trashed after calling a

subroutine.

*

All other registers must be preserved by the callee. Parameters are passed in

*

registers d1, d2, d3 ... (for data values) and a1, a2, a3 ... (for pointers) in

left

*

to right order. Stack frames are not used. All subroutines are non-re-entrant

and

*

so local variables are allocated as global variables at fixed RAM addresses.

Stack is

*

used sparingly where required to preserve specific register values. Numeric

results

*

are generally returned in register d1. Register d0 is often used to return an

error

*

code with $00 meaning success and anything else (often simply $FF) meaning

failure.

*

START OF CODE

START:

*

FIRMWARE COMPATIBILITY CHECK

*

*

This writes the firmware ID into the location at which it is normally stored

within the

*

firmware. This allows the MEMS3 Mapper S-Record loader code to verify that the

patch is

*

being applied to the firmware version for which it was written.

*

*

Many of addresses specified as constants within this file are specific to a

firmware

*

version. Constants annotated "Firmware ksr3p007 only!" are only

applicable to the

*

firmware version ksr3p007.

ADDR_FIRMWARE_ID: EQU $110400

ORG

ADDR_FIRMWARE_ID

DC.B 'kkssrr33pp000077' * Firmware ksr3p007 only!

*

CONSTANTS - BASE ADDRESSES

*

*

These constants declare the base addresses for the RAM and ROM blocks which we

have

*

chosen to use. They also declare the base address of the firmware vector table

which is

*

found at the very start of the firmware address space, the base address of the

map and

*

the base address for the table index in the map.

ADDR_BASE_RAM_DATA: EQU $1900 * Base RAM data

address. * Firmware ksr3p007 only!

ADDR_BASE_ROM_CODE: EQU $139040 * Base ROM code

address. * Firmware ksr3p007 only!

ADDR_BASE_VECTORS: EQU $110000 * Base address

for vectors.

*

CONSTANT - INITIALISATION PATCH ADDRESS

*

*

This constant declares the address within the firmware initialisation routine

where we

*

have chosen to patch in a call to our own initialisation routine.

PATCH_INI_JMP: EQU $115702 * Firmware

ksr3p007 only!

*

CONSTANTS - DATA FORMAT

*

*

These constants declare the data format to be used for communications. The

BAUD_RATE

*

should be chosen to be close to (ideally within 2% of) one which an FT232RL or

CH340G

*

cable can synthesize and such that 16,307,200 / 32 / BAUD_RATE is an integer.

The

*

PARITY constant combines appropriate values from PARITY_EVEN, PARITY_ODD,

*

PARITY_DISABLED and PARITY_ENABLED as required. The FRAME_BITS constant may be

set to

*

either FRAME_BITS_10 (e.g. 1 start bit, 8 data bits and 1 stop bit) or

FRAME_BITS_11

*

(e.g. 1 start bit, 8 data bits, 1 parity bit and 1 stop bit). The DATA_FORMAT

constant

*

then combines PARITY and FRAME_BITS.

BAUD_9600: EQU 9615

BAUD_19600: EQU 19600

BAUD_39200: EQU 39200

BAUD_85000: EQU 84933

BAUD_127400: EQU 127400

BAUD_256000: EQU 254800

BAUD_RATE: EQU BAUD_25600

PARITY_EVEN: EQU 0

PARITY_ODD: EQU $800

PARITY_DISABLED: EQU 0

PARITY_ENABLED: EQU $400

PARITY: EQU PARITY_EVEN|PARITY_ENABLED * Parity.

FRAME_BITS_10: EQU 0

FRAME_BITS_11: EQU $200

FRAME_BITS: EQU FRAME_BITS_11 * Bits.

DATA_FORMAT: EQU PARITY|FRAME_BITS

*

CONSTANTS - QSM REGISTER QMCR

*

*

These constants declare fields and values for use with the QSM module control

register

*

QMCR. These define the QSM configuration registers as lying within protected

supervisor

*

address space and set the QSM interrupt arbitration priority value to 7. These

are the

*

same values as are normally assigned by the firmware.

QSM_QMCR_SUP: EQU $80 * QSM registers

in supervisor space.

QSM_QMCR_IARB_7: EQU $07 * QSM interrupt

arbitration priority 7.

QSM_QMCR_VALUE: EQU QSM_QMCR_SUP|QSM_QMCR_IARB_7

*

CONSTANTS - QSM REGISTER QILR

*

*

These constants declare fields and values for use with the QSM interrupt level

register

*

QILR. These set the SCI interrupt level to 6, and the QSPI interrupt level to 0

(the

*

QSPI is unused). These are the same values as are normally assigned by the

firmware.

QSM_QILR_ILQSP: EQU 0 * QSPI unused,

interrupt level 0.

QSM_QILR_ILSCI: EQU $06 * SCI interrupt

level 6.

QSM_QILR_VALUE: EQU QSM_QILR_ILQSP|QSM_QILR_ILSCI

*

CONSTANTS - QSM REGISTER QIVR

*

*

These constants declare fields and values for use with the QSM interrupt vector

*

register QIVR. These set the SCI interrupt vector number to $50 (the QSPI

interrupt

*

vector number the automatically becomes $51 but is unused). These are the same

values

*

as are normally assigned by the firmware.

QSM_QIVR_INTV: EQU $50 * SCI interrupt

vector $50.

QSM_QIVR_VALUE: EQU QSM_QIVR_INTV

*

CONSTANTS - QSM REGISTER SCCR0

*

*

These constants declare fields and values for use with the QSM/SCI control

register

*

SCCR0. They set the Baud rate using a calculation based on the BAUD_RATE

constant

*

declared above.

QSM_SCCR0_SCBR: EQU 16307200/32/BAUD_RATE * Baud rate.

QSM_SCCR0_VALUE: EQU QSM_SCCR0_SCBR

*

CONSTANTS - QSM REGISTER SCCR1

*

*

These constants declare fields and values for use with the QSM/SCI control

register

*

SCCR1. They combine the DATA_FORMAT constant declared above with enable flags

for the

*

receiver, the transmitter and receiver interrupts by default (transmitter

interrupts

*

are enabled and disabled dynamically based on whether there is more data to be

sent).

QSM_SCCR1_RE: EQU $4 * RX enable.

QSM_SCCR1_TE: EQU $8 * TX enable.

QSM_SCCR1_RIE: EQU $20 * RX interrupt

enable.

QSM_SCCR1_TIE: EQU $80 * TX interrupt enable.

QSM_SCCR1_VALUE: EQU

DATA_FORMAT|QSM_SCCR1_RE|QSM_SCCR1_TE|QSM_SCCR1_RIE

*

CONSTANTS - QSM REGISTER ADDRESSES

*

*

These constants declare the memory addresses to which the QSM registers are

mapped.

*

QSM registers are accessed as though they were simply memory at the addresses

below.

QSM_BASE: EQU $FFFFFC00 * Base address of the QSM registers.

QSM_QMCR: EQU QSM_BASE * QSM module control register QMCR address.

QSM_QILR: EQU QSM_BASE+$04 * QSM interrupt level register QILR address.

QSM_QIVR: EQU QSM_BASE+$05 * QSM interrupt vector register QIVR address.

QSM_SCCR0: EQU QSM_BASE+$08 * QSM control register SCCR0 address.

QSM_SCCR1: EQU QSM_BASE+$0A * QSM control register SCCR1 address.

QSM_SCSR: EQU QSM_BASE+$0C * QSM status register SCSR address.

QSM_SCDR: EQU QSM_BASE+$0E * QSM data register SCDR address.

*

CONSTANTS - QUEUE SIZES

*

*

These constants declare the sizes of the receive and transmit queues in bytes.

These

*

are the actual numbers of bytes which may be queued and not the overall sizes

of the

*

structures including their control fields, which are 6 bytes larger.

RX_QUEUE_SIZE: EQU $20 * RX queue size in bytes.

TX_QUEUE_SIZE: EQU $80 * TX queue size in bytes.

*

RAM DATA

ORG ADDR_BASE_RAM_DATA

*

RAM VARIABLES - RECEIVE AND TRANSMIT QUEUES

*

*

The labels below identify the locations of the receive and transmit queue

structures

*

in RAM. These use the DS.B directive to define them as storage locations

without

*

specifying the contents. It is important that the assembled .S68 file does not

contain

*

data for locations which lie outside of the firmware memory address space as

the MEMS3

*

Mapper application will reject .S68 files which do.

_rx_queue: DS.B RX_QUEUE_SIZE+6 * RX queue structure.

_tx_queue: DS.B TX_QUEUE_SIZE+6 * TXT queue structure.

*

RAM VARIABLES - LOCAL VARIABLES - QUERY STATUS FOR RX OR TX QUEUE

*

*

The labels below identify the locations used for local variables for the

_queue_status

*

subroutine. Local variable use fixed locations in preference to being allocated

on

*

the stack as the stack is small and this subroutine is not re-entrant.

_queue_status_w_in: DS.W 1

_queue_status_w_full: DS.W 1

_queue_status_w_out: DS.W 1

*

RAM VARIABLES - LOCAL VARIABLES - QSM/SCI INTERRUPT VECTOR

*

*

The labels below identify the locations used for local variables for the

_sci_interrupt

*

subroutine. Local variable use fixed locations in preference to being allocated

on

*

the stack as the stack is small and this subroutine is not re-entrant.

_sci_interrupt_w_scsr: DS.W 1

_sci_interrupt_w_scdr: DS.W 1

_sci_interrupt_w_in: DS.W 1

_sci_interrupt_w_full: DS.W 1

_sci_interrupt_w_out: DS.W 1

_sci_interrupt_l_infull: DS.L 1

*

RAM VARIABLES - LOCAL VARIABLES - READ BYTE FROM RX QUEUE

*

*

The labels below identify the locations used for local variables for the

_rx_byte

*

subroutine. Local variable use fixed locations in preference to being allocated

on

*

the stack as the stack is small and this subroutine is not re-entrant.

_rx_byte_w_in: DS.W 1

_rx_byte_w_full: DS.W 1

_rx_byte_w_out: DS.W 1

_rx_byte_l_fullout: DS.L 1

*

RAM VARIABLES - LOCAL VARIABLES - WRITE BYTE TO TX QUEUE

*

*

The labels below identify the locations used for local variables for the

_tx_byte

*

subroutine. Local variable use fixed locations in preference to being allocated

on

*

the stack as the stack is small and this subroutine is not re-entrant.

_tx_byte_b_txbyte: DS.W 1

_tx_byte_w_in: DS.W 1

_tx_byte_w_full: DS.W 1

_tx_byte_w_out: DS.W 1

_tx_byte_l_infull: DS.L 1

*

ROM CODE

ORG

ADDR_BASE_ROM_CODE

*

FREESCALE SCI BUFFER LIBRARY FUNCTIONS

*

*

The library functions _sci_initialise, _sci_interrupt, _queue_initialise,

*

_queue_status, _rx_byte and _tx_byte below represent a reworking of the code

from the

*

Freescale Application Node AN1724 "Implementing SCI Receive and Transmit

Buffers in

*

C" at https://www.nxp.com/docs/en/application-note/AN1724.pdf. This code

was compiled

*

to 68000 assembly language using Compiler Explorer: https://franke.ms/cex/,

compiling

*

for Amiga using the g++-10.2.1b compiler settings. The code was then edited by

hand

*

as required to make it compatible with EASy68K.

*

INITIALISE QSM/SCI

*

*

The _sci_initialise subroutine initialises the QSM, QILR, QIVR, SCCR0 and SCCR1

*

registers of the QSM with constant values declared above. See the comments for

the

*

various constant blocks above for further information.

*

*

PARAMETERS:

* Void.

*

RETURNS:

* Void.

_sci_initialise:

move.w

#QSM_QMCR_VALUE,(QSM_QMCR) * Initialise QSM

register QMCR.

move.b

#QSM_QILR_VALUE,(QSM_QILR) * Initialise QSM

register QILR.

move.b

#QSM_QIVR_VALUE,(QSM_QIVR) * Initialise QSM

register QIVR.

move.w

#QSM_SCCR0_VALUE,(QSM_SCCR0) * Initialise QSM

register SCCR0.

move.w

#QSM_SCCR1_VALUE,(QSM_SCCR1) * Initialise QSM

register SCCR1.

rts

*

QSM/SCI INTERRUPT VECTOR

*

*

The _sci_interrupt subroutine forms the interrupt vector for the QSM/SCI. This

is used

*

to completely replace the interrupt vector subroutine in the firmware by

patching the

*

entry in the firmware vector table. This subroutine was initially compiled from

C as

*

described above, then edited by hand for compatibility. In particular the

MOVEM, LINK

*

and UNLK instructions were added and RTS was replaced with RTE in order to make

the

*

compiled subroutine compatible with being an interrupt vector. Stack frames

were

*

removed and stack local storage was replaced with fixed RAM addresses.

*

*

PARAMETERS:

* Void.

*

RETURNS:

* Void.

_sci_interrupt:

REG_SCI_INT: REG d0-d1/a0-a1 * Save registers (INTERRUPT: preserves

ALL).

movem.l

REG_SCI_INT,-(sp) * SR preserved

implicitly.

move.w

#QSM_SCSR,a0

move.w

(a0),(_sci_interrupt_w_scsr)

moveq

#0,d0

move.w

(_sci_interrupt_w_scsr),d0

moveq

#64,d1

and.l

d1,d0

tst.l

d0

beq

_sci_interrupt_4

move.w

#QSM_SCDR,a0

move.w

(a0),(_sci_interrupt_w_scdr)

moveq

#0,d0

move.w

(_sci_interrupt_w_scsr),d0

moveq

#8,d1

and.l

d1,d0

tst.l

d0

bne

_sci_interrupt_10

move.w

_rx_queue,(_sci_interrupt_w_in)

move.w

2+_rx_queue,(_sci_interrupt_w_full)

move.w

4+_rx_queue,(_sci_interrupt_w_out)

move.w

(_sci_interrupt_w_in),d0

cmp.w

(_sci_interrupt_w_out),d0

bne

_sci_interrupt_1

tst.w

(_sci_interrupt_w_full)

bne

_sci_interrupt_10

_sci_interrupt_1:

moveq

#0,d0

move.w

(_sci_interrupt_w_in),d0

move.w

(_sci_interrupt_w_scdr),d1

lea

6+_rx_queue,a0

move.l

d0,a1

move.b

d1,(0,a1,a0.l)

move.w

(_sci_interrupt_w_in),d0

addq.w

#1,d0

move.w

d0,(_sci_interrupt_w_in)

cmp.w

#RX_QUEUE_SIZE-1,(_sci_interrupt_w_in)

bls

_sci_interrupt_2

clr.w

(_sci_interrupt_w_in)

_sci_interrupt_2:

move.w

(_sci_interrupt_w_in),d0

cmp.w

(_sci_interrupt_w_out),d0

bne

_sci_interrupt_3

moveq

#0,d0

move.w

(_sci_interrupt_w_out),d0

swap

d0

clr.w

d0

moveq

#1,d1

or.l

d1,d0

move.l

d0,(_sci_interrupt_l_infull)

lea

_rx_queue,a0

move.l

(_sci_interrupt_l_infull),(a0)

bra

_sci_interrupt_10

_sci_interrupt_3:

move.w

(_sci_interrupt_w_in),_rx_queue

bra

_sci_interrupt_10

_sci_interrupt_4:

moveq

#0,d0

move.w

(_sci_interrupt_w_scsr),d0

moveq

#8,d1

and.l

d1,d0

tst.l

d0

beq

_sci_interrupt_5

move.w

#QSM_SCDR,a0

move.w

(a0),(_sci_interrupt_w_scdr)

bra

_sci_interrupt_10

_sci_interrupt_5:

moveq

#0,d0

move.w

(_sci_interrupt_w_scsr),d0

and.l

#256,d0

tst.l d0

beq

_sci_interrupt_9

move.w

_tx_queue,(_sci_interrupt_w_in)

move.w

2+_tx_queue,(_sci_interrupt_w_full)

move.w

4+_tx_queue,(_sci_interrupt_w_out)

move.w

(_sci_interrupt_w_in),d0

cmp.w

(_sci_interrupt_w_out),d0

bne

_sci_interrupt_6

tst.w

(_sci_interrupt_w_full)

beq

_sci_interrupt_8

_sci_interrupt_6:

moveq

#0,d0

move.w

(_sci_interrupt_w_out),d0

lea

6+_tx_queue,a0

move.l

d0,a1

move.b

(0,a1,a0.l),d0

move.b

d0,d0

and.w

#255,d0

move.w

d0,(_sci_interrupt_w_scdr)

move.w

(_sci_interrupt_w_out),d0

addq.w

#1,d0

move.w

d0,(_sci_interrupt_w_out)

cmp.w

#TX_QUEUE_SIZE-1,(_sci_interrupt_w_out)

bls

_sci_interrupt_7

clr.w

(_sci_interrupt_w_out)

_sci_interrupt_7:

moveq

#0,d0

move.w

(_sci_interrupt_w_out),d0

move.l

d0,(_sci_interrupt_l_infull)

lea

2+_tx_queue,a0

move.l

(_sci_interrupt_l_infull),(a0)

move.w

#QSM_SCDR,a0

move.w

(_sci_interrupt_w_scdr),(a0)

bra

_sci_interrupt_10

_sci_interrupt_8:

move.w

#QSM_SCCR1,a0

move.w

#QSM_SCCR1_VALUE,(a0)

bra

_sci_interrupt_10

_sci_interrupt_9:

bsr

_sci_initialise

_sci_interrupt_10:

movem.l

(sp)+,REG_SCI_INT * Restore

registers.

rte

*

INITIALISE RX OR TX QUEUE

*

*

The _queue_initialise subroutine is called to initialise a queue structure

(either the

*

receive or transmit queue). This subroutine was initially compiled from C as

described

*

above, then edited by hand for compatibility. Stack frames were removed and

stack

*

local storage was replaced with fixed RAM addresses.

*

*

PARAMETERS:

* Address of queue (Long) in a1.

*

RETURNS:

* Void.

_queue_initialise:

move.w

#2,(a1)

clr.w

(2,a1)

move.w

#2,(4,a1)

rts

*

QUERY STATUS FOR RX OR TX QUEUE

*

*

The _queue_status subroutine is called to query the number of bytes currently

queued in

*

a queue structure (either the receive or transmit queue). This subroutine was

initially

*

compiled from C as described above, then edited by hand for compatibility.

Stack frames

*

were removed and stack local storage was replaced with fixed RAM addresses.

*

*

PARAMETERS:

* Address of queue (Long) in a1.

* Size of queue (Word) in d1.

*

RETURNS:

* Word in d0.

_queue_status:

move.w

(a1),(_queue_status_w_in)

move.w

(2,a1),(_queue_status_w_full)

move.w

(4,a1),(_queue_status_w_out)

move.w

(_queue_status_w_in),d0

cmp.w

(_queue_status_w_out),d0

bls

_queue_status_1

move.w

(_queue_status_w_in),d0

sub.w

(_queue_status_w_out),d0

bra

_queue_status_4

_queue_status_1:

move.w

(_queue_status_w_in),d0

cmp.w

(_queue_status_w_out),d0

bcc

_queue_status_2

move.w

d1,d0

sub.w

(_queue_status_w_out),d0

add.w

(_queue_status_w_in),d0

bra

_queue_status_4

_queue_status_2:

tst.w

(_queue_status_w_full)

beq

_queue_status_3

move.w

d1,d0

bra

_queue_status_4

_queue_status_3:

clr.w

d0

_queue_status_4:

rts

*

READ BYTE FROM RX QUEUE

*

*

The _rx_byte subroutine is called to get the next received byte queued from the

*

receive queue. This subroutine was initially compiled from C as described

above, then

*

edited by hand for compatibility. Stack frames were removed and stack local

storage

*

was replaced with fixed RAM addresses.

*

*

PARAMETERS:

* Address of byte (Long) in a1.

*

RETURNS:

* Byte ($00 Success, $FF Failure) in d0.

_rx_byte:

move.w

_rx_queue,_rx_byte_w_in

move.w

2+_rx_queue,_rx_byte_w_full

move.w

4+_rx_queue,_rx_byte_w_out

move.w

_rx_byte_w_in,d0

cmp.w

_rx_byte_w_out,d0

bne

_rx_byte_1

tst.w

_rx_byte_w_full

beq

_rx_byte_3

_rx_byte_1:

moveq

#0,d0

move.w

_rx_byte_w_out,d0

lea

6+_rx_queue,a0

move.l

d0,a1

move.b

(0,a1,a0.l),d0

move.l

a1,a0

move.b

d0,(a0)

move.w

_rx_byte_w_out,d0

addq.w

#1,d0

move.w

d0,_rx_byte_w_out

cmp.w

#RX_QUEUE_SIZE-1,_rx_byte_w_out

bls

_rx_byte_2

clr.w

_rx_byte_w_out

_rx_byte_2:

moveq

#0,d0

move.w

_rx_byte_w_out,d0

move.l

d0,_rx_byte_l_fullout

lea

2+_rx_queue,a0

move.l

_rx_byte_l_fullout,(a0)

clr.b

d0

bra

_rx_byte_4

_rx_byte_3:

moveq

#$FF,d0

_rx_byte_4:

rts

*

WRITE BYTE TO TX QUEUE

*

*

The _tx_byte subroutine is called to send the next transmitted byte queued to

the

*

transmit queue. The byte is queued for future background transmission under

interrupt

*

control and this routine returns immediately without waiting for the

transmission to

*

complete. This subroutine was initially compiled from C as described above,

then edited

*

by hand for compatibility. Stack frames were removed and stack local storage

was

*

replaced with fixed RAM addresses.

*

*

PARAMETERS:

* Byte (Word) in d1.

*

RETURNS:

* Byte ($00 Success, $FF Failure) in d0.

_tx_byte:

move.w

d1,d0

move.b

d0,_tx_byte_b_txbyte

move.w

_tx_queue,_tx_byte_w_in

move.w

2+_tx_queue,_tx_byte_w_full

move.w

4+_tx_queue,_tx_byte_w_out

move.w

_tx_byte_w_in,d0

cmp.w

_tx_byte_w_out,d0

bne

_tx_byte_1

tst.w

_tx_byte_w_full

bne

_tx_byte_5

_tx_byte_1:

moveq

#0,d0

move.w

_tx_byte_w_in,d0

lea

6+_tx_queue,a0

move.l

d0,a1

move.b

_tx_byte_b_txbyte,(0,a1,a0.l)

move.w

_tx_byte_w_in,d0

addq.w

#1,d0

move.w

d0,_tx_byte_w_in

cmp.w

#TX_QUEUE_SIZE-1,_tx_byte_w_in

bls

_tx_byte_2

clr.w

_tx_byte_w_in

_tx_byte_2:

move.w

_tx_byte_w_in,d0

cmp.w

_tx_byte_w_out,d0

bne

_tx_byte_3

moveq

#0,d0

move.w

_tx_byte_w_out,d0

swap

d0

clr.w

d0

moveq

#1,d1

or.l

d1,d0

move.l

d0,_tx_byte_l_infull

lea

_tx_queue,a0

move.l

_tx_byte_l_infull,(a0)

bra

_tx_byte_4

_tx_byte_3:

move.w

_tx_byte_w_in,_tx_queue

_tx_byte_4:

move.w

#QSM_SCCR1,a0

move.w

#QSM_SCCR1_VALUE|QSM_SCCR1_TIE,(a0)

clr.b

d0

bra

_tx_byte_6

_tx_byte_5:

moveq

#$FF,d0

_tx_byte_6:

rts

*

PATCH ROUTINE FOR INITIALISATION

*

*

The _patch_initialise subroutine initialises the debug patch. It is called from

the

*

main firmware initialisation routine by overwriting a MOVE.B #0,($FFFFFA1F).W

*

instruction with JSR _PATCH_INITIALISE. The _patch_initialise subroutine then

*

executes the relocatable instruction which was overwritten then proceeds to

perform

*

its own initialisation tasks.

*

*

PARAMETERS:

* Void.

*

RETURNS:

* Void.

_patch_initialise:

OPT NOWAR * Execute

instruction replaced by patch.

move.b

#0,($FFFFFA1F).w

OPT WAR

REG_PATCH_INI: REG d0-d1,ao-a1,sr * Save registers (PATCH: Preserves ALL).

movem.l

REG_PATCH_INI,-(sp) * Non-scratch

registers preserved by subroutines.

move.l

#_rx_queue,a1 * Initialise RX

queue.

bsr

_queue_initialise

move.l

#_tx_queue,a1 * Initialise TX

queue.

bsr

_queue_initialise

bsr

_sci_initialise * Initialise

QSM/SCI.

move.w

#'H',d1 * Test code.

bsr

_tx_byte

move.w

#'e',d1

bsr

_tx_byte

move.w

#'l',d1

bsr

_tx_byte

move.w

#'l',d1

bsr

_tx_byte

move.w

#'o',d1

bsr

_tx_byte

move.w

#' ',d1

bsr

_tx_byte

move.w

#'W',d1

bsr

_tx_byte

move.w

#'o',d1

bsr

_tx_byte

move.w

#'r',d1

bsr

_tx_byte

move.w

#'l',d1

bsr

_tx_byte

move.w

#'d',d1

bsr

_tx_byte

move.w

#'!',d1

bsr

_tx_byte

movem.l

(sp)+,REG_PATCH_INI * Restore

registers.

rts

*

APPLY PATCH - DISABLE NATIVE QSM/SCI ACCESS

*

*

The instructions below are patched into specific locations within the firmware

to

*

effectively disable access to the QSM/SCI. RTS instructions are used to replace

*

existing instructions in order to force early return from a subroutine. In most

*

cases the first instruction of the subroutine is replaced, disabling the

subroutine

*

entirely.

ORG $118C26 * Subroutines, return with RTS. * Firmware ksr3p007 only!

rts

ORG $1116D0

rts

ORG $1116D6

rts

ORG $116AF6

rts

ORG $118C92

rts

ORG $132C8A

rts

*

APPLY PATCH - REPLACE QSI/SCM INTERRUPT VECTOR

*

*

The _sci_interrupt subroutine forms the interrupt vector for the QSM/SCI. This

is used

*

to completely replace the interrupt vector subroutine in the firmware by

patching the

*

entry in the firmware vector table.

ORG

ADDR_BASE_VECTORS+(QSM_QIVR_INTV*4)

DC.L _sci_interrupt

*

APPLY PATCH - INITIALISATION

*

*

The _patch_initialise subroutine initialises the debug patch. It is called from

the

*

main firmware initialisation routine by overwriting a MOVE.B #0,($FFFFFA1F).W